# Chapter 6

# PN Junction Diode

version 2.0 (updated: July 31, 2012), ©Prentice Hall

#### Outline

- 6.1 The ideal PN junction diode

- 6.2 Ideal PN diode in thermal equilibrium

- 6.3 Current-voltage characteristics of the ideal PN diode

- 6.3.1 Electrostatics under bias

- 6.3.2 I-V characteristics: qualitative discussion

- 6.3.2 I-V characteristics: quantitative models

- 6.4 Charge-voltage characteristics of ideal PN diode

- 6.4.1 Depletion capacitance

- 6.4.2 Minority carrier storage

- 6.5 Equivalent circuit models of the ideal PN diode

- 6.6 Non-ideal and second-order effects

- 6.6.1 Short diode

- 6.6.2 Space-charge-region generation and recombination

- 6.6.3 Series resistance

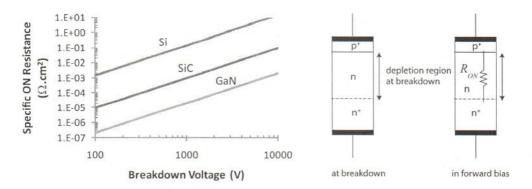

- 6.6.4 Breakdown voltage

- 6.6.5 Non-uniform doping distributions

- 6.6.6 High-injection effects

- 6.7 Integrated PN diode

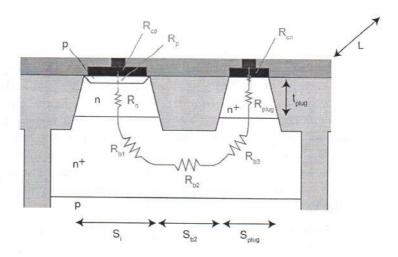

- 6.7.1 Isolation

- 6.7.2 Series resistance

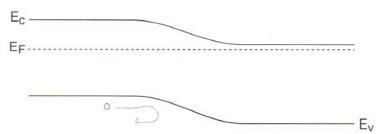

- 6.7.3 High-low junction

- 6.8 Summary

- 6.9 Further reading

### Advanced Topics

- AT6.1 Quasi-neutral region resistance in ideal diode

- AT6.2 Equivalent circuit model for circuit design

- AT6.3 Switching characteristics of PN diode

#### Problems

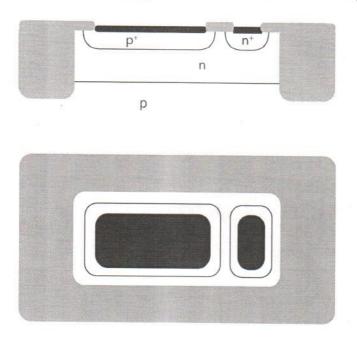

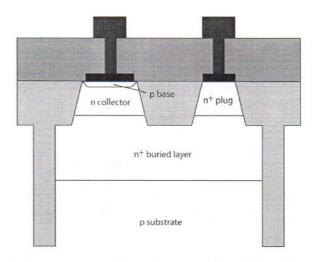

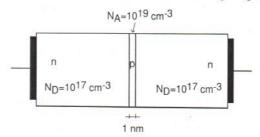

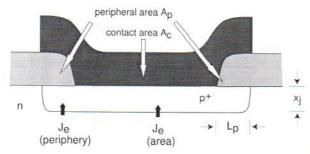

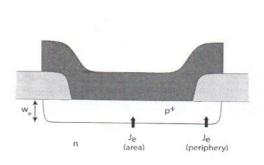

Figure 6.1: Cross section and top view of integrated PN junction diode.

The PN junction diode (or simply "PN diode") is the first microelectronics device that we study in detail in this book. The PN diode is a two-terminal device that exploits the *rectifying characteristics* of a PN junction. What this means is that under a certain voltage polarity, current readily flows across the device, while for the reverse polarity, the device is essentially open.

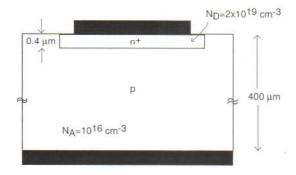

A top view and cross-sectional view of an integrated PN diode is shown in Fig. 6.1. It consists of a  $p^+$  region created inside an n-type well fabricated on a p-type wafer. The contact to the n-type well is made through an  $n^+$  region. The p region is often called the *anode* and the n region is referred to as the *cathode*.

PN diodes are very useful in many applications. They are, for example, used to provide electrostatic discharge (ESD) protection in input/output circuitry of integrated circuits. They also perform a variety of functions in analog circuits and power electronics. A number of other familiar semiconductor devices are in essence PN diodes. Examples are solar cells, light-emitting diodes and laser diodes.

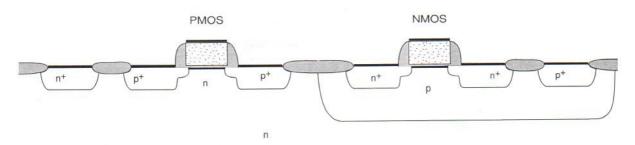

In addition, PN junctions themselves are present in virtually every microelectronic device. For example, two PN junctions back-to-back constitute the essence of the bipolar junction transistor, a very important device that we will study in detail in Ch. 11. A Complementary Metal-Oxide-Semiconductor (CMOS) transistor pair also includes several PN junctions, as can be seen in Fig. 6.2. Finally, and this is perhaps their most widespread application, reverse biased PN junctions exhibit excellent isolation properties and are therefore employed in integrated circuits to isolate devices from each other. An example is seen in Fig. 6.1 where the n-well/p-substrate junction isolates the PN diode from the rest of the devices on the wafer.

This chapter deals with the physics of the PN junction and the PN junction diode. These are

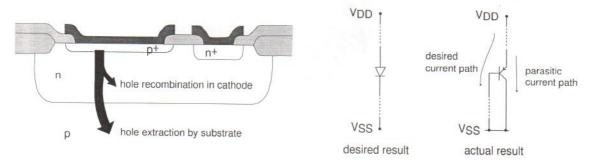

Figure 6.2: Cross section of a Complementary Metal-Oxide-Semiconductor (CMOS) transistor pair showing several PN junctions that naturally occur in this structure.

minority-carrier-type structures. In our analysis, we will heavily draw from our earlier study of minority-carrier type transport of Ch. 5. Since minority carrier behavior is also at the heart of bipolar transistor operation, some of the materials that we develop in this chapter will reappear in Ch. 11.

This chapter is organized as follows. We start by defining the notion of the ideal PN junction diode. We follow this with an analysis of the PN diode in thermal equilibrium. We then discuss the consequences of driving the PN junction out of equilibrium through the application of a bias. This culminates with the derivation of the rectifying current-voltage characteristics of the PN junction. The rest of the chapter is devoted to studying in detail the PN junction diode: equivalent circuit models, parasitics, second-order effects and design considerations. The large-signal dynamics of the PN diode receive special attention as they are distinctly different in nature from those of the other kind of diode, the Schottky diode that we study in Ch. 7. We will understand the reasons behind the relatively slow dynamic response of PN diodes that makes them unsuitable for many high-frequency applications.

This is a key chapter in this book. Important concepts presented earlier are encountered again here but now in a device context. New concepts are also introduced that will reappear later on in different chapters.

## 6.1 The ideal PN junction diode

It is useful to define the notion of an ideal PN junction diode. This is a concept device with a simple geometry, simplified physics and no parasitics that captures the essence of the PN diode. We define this model device in this section and then analyze it in the following sections. At the end of this chapter, we will study the most significant non idealities and the parasitics that affect real PN diodes.

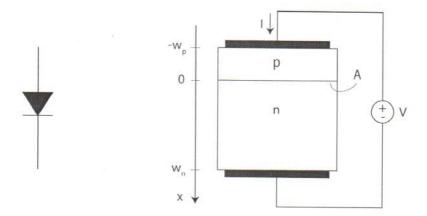

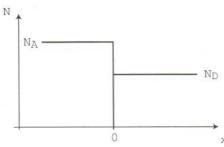

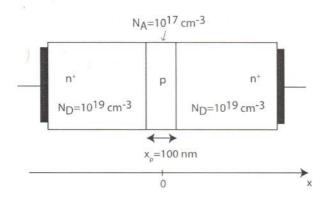

Fig. 6.3 shows the circuit symbol of a PN diode and a sketch of an ideal diode. This consists of a p-region with doping level  $N_A$  on top of an n region with doping level  $N_D$ . The transition between p-type and n-type is perfectly abrupt. Each region is electrically accessed through an ohmic contact. This device stands alone and is completely isolated from the rest of the world.

In the analysis of the ideal PN diode, we will make a number of approximations. Some of

Figure 6.3: Left: circuit symbol for PN diode. Right: sketch of ideal PN diode.

these will be "undone" later on in this chapter. These are our simplifying assumptions:

- All carrier flow is one dimensional. There are no 2D or 3D effects.

- Doping levels are uniform throughout (we study the impact of non-uniform doping levels in Sec. 6.6.5).

- We treat the p-n transition region under the so-called depletion approximation. We consider

the rest of the semiconductor on both sides as quasi-neutral regions. This is explained below.

- We assume that the quasi-neutral regions are much longer than the respective minority carrier diffusion lengths (we call this a "long" diode; a "short" diode in which the quasi-neutral regions are much shorter than the diffusion lengths is discussed in Sec. 6.6.1).

- We assume non-degenerate statistics for electrons and holes everywhere.

- Under conditions of excess carriers, low-level injection prevails at all times in all regions (some of the implications of high-level injection are examined in Sec. 6.6.6).

- We neglect generation and recombination of carriers in the depletion region (this is added in Sec. 6.6.2).

- We ignore any resistance effects from the semiconductor regions or the ohmic contacts (we study the impact of parasitic resistance in Sec. 6.6.3).

- We assume ideal ohmic contacts as defined in Sec. 5.2.2.

- We ignore any effects associated with the sidewalls of the device.

Fig. 6.3 defines the axis that we will use to analyze the PN diode. Since we assume this one to be a one-dimensional situation, there is only one axis to consider. We place its origin at the so-called *metallurgical junction* where the semiconductor changes from p-type to n-type. The extent of the p region is  $w_p$ . The extent of the n region is  $w_n$ . The area of the junction is A.

J. A. del Alamo 321

The voltage and current notation are also shown in Fig. 6.3. We always define the applied voltage with the p region positive with respect to the n region. When V > 0, the PN diode is under forward bias. When V < 0, the PN diode is under reverse bias. The current entering the p region is defined as positive. This notation is consistent with a naming convention for the two regions that is not widely used. The p region is at times called *anode* while the n-region is denoted as *cathode*.

### 6.2 Ideal PN junction in thermal equilibrium

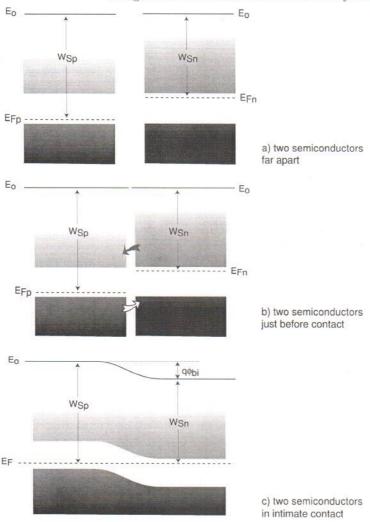

A good place to start the analysis of the ideal PN diode is with an analysis of the structure in thermal equilibrium. We can envision creating such a situation by bringing together a p and an n region in intimate contact so that charge redistribution can take place. Fig. 6.4 sketches what happens. Isolated, the n-side contains lots of electrons and very few holes. The p-side, on the other hand, has many holes and very few electrons. A different way of looking at this is that the conduction band on the n-side is populated with lots of electrons, while that on the p-side is rather empty. Similarly, the valence band on the p-side has a sizable amount of holes while that on the n-side has very few.

Once intimate contact is established, electrons on the n-side will tend to flow towards the p-side since they are presented with empty states at the same energy. At the same time, holes on the p-side will flow towards the n-side where there are lots of available states at the same energy. We can alternatively view this intermingling of carriers as being driven by diffusion, since there are more carriers of one type on each side of the junction. While this view works well in this particular case, in general it is not a sure way to argue the sense of carrier redistribution. The energy view always provides a good understanding of the sense of carrier redistribution.

As this carrier intermingling proceeds, two things happen. First, electron-hole recombination takes place. Second and more important for us here, an electric field develops as the ionized acceptors and donors have their charge uncompensated by their respective majority carriers. The more carrier diffusion takes place, the higher the electric field. It is this electric field that eventually brings the diffusion process to a halt by introducing a drift force on the carriers that precisely compensates their diffusion tendency.

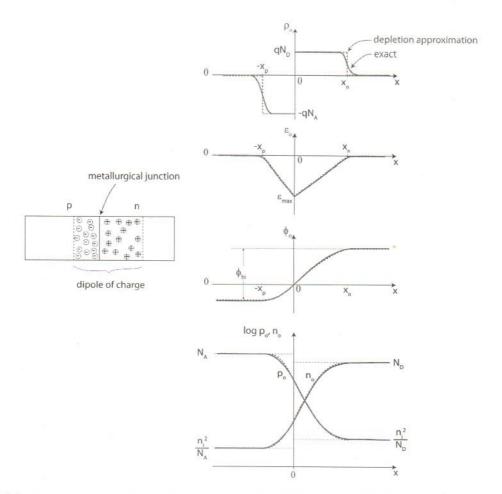

Once thermal equilibrium has been established and charge redistribution has stopped, a charge dipole has developed across the metallurgical junction. Sufficiently far away on either side of the junction, bulk conditions ought to prevail and the majority carrier concentrations equal the respective doping concentrations. In the vicinity of the junction, the n-side has less electrons and more holes than when it was isolated. The situation is reversed on the p-side. This results in net positive charge on the n-side and net negative charge on the p-side, as sketched in Fig. 6.5. This dipole of charge produces an electric field which results in a potential energy that must be added to the energy band diagram. The magnitude and spatial distribution of the electric field has to be such as to make the Fermi level flat everywhere, as sketched in Fig. 6.4.

The dipole of charge at the metallurgical interface of a PN junction results in a built-in potential  $\phi_{bi}$ . The energy band diagram of Fig. 6.4 allows us to easily calculate  $\phi_{bi}$ . Let us place

Figure 6.4: Formation of the energy band diagram of a PN junction in thermal equilibrium. Top: the p- and n-regions isolated from each other. Bottom: after contact has been established and equilibrium has been reached.

the coordinate origin x=0 at the metallurgical junction and denote  $x\gg 0$  and  $x\ll 0$  as the n-and p-regions sufficiently far away from the junction so that bulk conditions prevail. Then:

$$q\phi_{bi} = W_{Sp} - W_{Sn} = (E_C - E_F)|_{x \ll 0} - (E_C - E_F)|_{x \gg 0}$$

$$= kT \ln \frac{N_c}{n_o(x \ll 0)} - kT \ln \frac{N_c}{n_o(x \gg 0)} = kT \ln \frac{n_o(x \gg 0)}{n_o(x \ll 0)}$$

(6.1)

Far away on the right where bulk conditions exist, electrons are majority carriers. Hence:  $n_o(x \gg 0) = N_D$ . Similarly far away on the left,  $n_o(x \ll 0) = n_i^2/N_A$ . Inserting this in Eq. 6.1, we get:

$$\phi_{bi} = \frac{kT}{q} \ln \frac{N_D N_A}{n_i^2} \tag{6.2}$$

It is important to recognize the limits to the validity of this expression. Three implicit assumptions were made in its derivation. First, it was assumed that both regions are extrinsic, that is, that  $N_D \gg n_i$  and  $N_A \gg n_i$ . This is always the case near room temperature. Second, all dopants were assumed to be ionized, also a good approximation for Si at room temperature if common dopants are utilized. Finally, in Eq. 6.1 Maxwell-Boltzmann statistics were utilized. This actually is not a good assumption in many practical PN junctions in which often one side is heavily doped. In this case, Fermi-Dirac statistics and heavy-doping effects, as described in Advanced Topic AT2.6, must be taken into account. When heavy doping effects are important,  $\phi_{bi}$  is slightly modified from the result given in Eq. 6.2. However, as a result of the presence of the logarithmic term, the difference is small and in general the error incurred in using Eq. 6.2 is acceptable for most applications.

Examining the volume charge density distribution in a PN junction in thermal equilibrium in Fig. 6.5, one can distinguish three different regions. Around the metallurgical junction, there is a space-charge region (SCR). On both sides of the SCR, there are two quasi-neutral regions (QNR), one p-type and the other n-type. Deep in the QNR's,  $\rho \simeq 0$ . As we advance towards the metallurgical junction from the n side, the electron concentration drops and the hole concentration increases. Since electrons are majority carriers, the drop of  $n_o$  is more significant from a charge point of view than the rise of  $p_o$ , and there is net positive charge due to the exposed donor atoms. Hence  $\rho \simeq qN_D$ . A similar situation occurs on the p side of the junction where  $\rho \simeq -qN_A$ right next to the metallurgical junction. Because of the exponential dependence of the carrier concentration on the electrostatic potential, the transition between the QNR's and the SCR is fairly sharp.

This understanding suggests that an approximate model to the electrostatics of the PN junction in equilibrium can be obtained by performing what is called the depletion approximation. This approximation assumes that the two quasi-neutral regions are perfectly charge neutral and that the space-charge region is perfectly devoid of carriers, i.e., depleted. Mathematically, this can be expressed as:

$$\rho_o(x) \simeq 0 \qquad \text{in p-QNR: } x < -x_p \qquad (6.3)$$

$$\rho_o(x) \simeq -qN_A \qquad \text{in SCR: } -x_p < x < 0 \qquad (6.4)$$

$$\rho_o(x) \simeq qN_D \qquad \text{in SCR: } 0 < x < x_n \qquad (6.5)$$

$$\rho_o(x) \simeq -qN_A \quad \text{in SCR: } -x_p < x < 0$$

(6.4)

$$\rho_o(x) \simeq qN_D \quad \text{in SCR: } 0 < x < x_n$$

(6.5)

$$\rho_o(x) \simeq 0$$

in n-QNR:  $x_n < x$  (6.6)

In these equations, the subindex "o" indicates thermal equilibrium. The location of the edges of the SCR,  $-x_p$  and  $x_n$ , is determined below.

Within the depletion approximation, models for the electrostatics of the PN junction are easy to obtain. Integration of this volume charge yields the electric field profile:

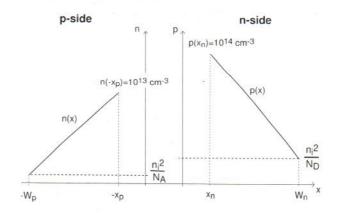

Figure 6.5: Electrostatics of a PN junction in thermal equilibrium. From top to bottom: volume charge density, electric field, electrostatic potential, and equilibrium carrier concentration. The continuous line is the exact solution. The discontinuous line is the calculation following the depletion approximation.

$$\mathcal{E}_o(x) \simeq 0$$

in p-QNR:  $x \leq -x_p$  (6.7)

$$\mathcal{E}_{o}(x) \simeq 0$$

in p-QNR:  $x \leq -x_{p}$  (6.7)

$\mathcal{E}_{o}(x) \simeq -\frac{qN_{A}}{\epsilon}(x+x_{p})$  in SCR:  $-x_{p} \leq x \leq 0$  (6.8)

$\mathcal{E}_{o}(x) \simeq \frac{qN_{D}}{\epsilon}(x-x_{n})$  in SCR:  $0 \leq x \leq x_{n}$  (6.9)

$\mathcal{E}_{o}(x) \simeq 0$  in n-QNR:  $x_{n} \leq x$  (6.10)

$$\mathcal{E}_o(x) \simeq \frac{qN_D}{\epsilon}(x - x_n)$$

in SCR:  $0 \le x \le x_n$  (6.9)

$$\mathcal{E}_o(x) \simeq 0$$

in n-QNR:  $x_n \leq x$  (6.10)

One more integration yields the electrostatic potential. Selecting  $\phi(x=0)=0$ , as reference:

$$\phi_o(x) \simeq -\frac{qN_A x_p^2}{2\epsilon}$$

in p-QNR:  $x \le -x_p$  (6.11)

$$\phi_o(x) \simeq \frac{qN_A}{2\epsilon}(x^2 + 2x_p x)$$

in SCR:  $-x_p \le x \le 0$  (6.12)

$$\phi_o(x) \simeq -\frac{qN_D}{2\epsilon}(x^2 - 2x_n x) \quad \text{in SCR: } 0 \le x \le x_n$$

(6.13)

$$\phi_o(x) \simeq \frac{qN_Dx_n^2}{2\epsilon}$$

in n-QNR:  $x_n \le x$  (6.14)

$x_n$  and  $x_p$  are obtained by demanding that two conditions be met. First, overall charge neutrality must be satisfied since each of the starting pieces of semiconductor were charge neutral and we have not allowed any particles to escape. This implies that:

$$qN_A x_p = qN_D x_n (6.15)$$

Second, the total electrostatic potential difference across the entire structure must equal the built-in potential derived above in Eq. 6.2. This results in:

$$\phi_o(x_n) - \phi_o(-x_p) = \frac{qN_D x_n^2}{2\epsilon} + \frac{qN_A x_p^2}{2\epsilon} = \phi_{bi}$$

(6.16)

Solving in these two equations for  $x_n$  and  $x_p$ , we get:

$$x_n = \sqrt{\frac{2\epsilon N_A \phi_{bi}}{q N_D (N_D + N_A)}} \tag{6.17}$$

$$x_p = \sqrt{\frac{2\epsilon N_D \phi_{bi}}{q N_A (N_D + N_A)}} \tag{6.18}$$

The total extent of the SCR, the sum  $x_n + x_p$  is:

$$x_{SCR} = \sqrt{\frac{2\epsilon(N_D + N_A)\phi_{bi}}{qN_AN_D}}$$

(6.19)

The maximum electric field occurs at the metallurgical junction and is easily found from Eq. 6.8 or 6.9 at x=0:

$$|\mathcal{E}_{o,max}| = \sqrt{\frac{2qN_A N_D \phi_{bi}}{\epsilon (N_D + N_A)}}$$

(6.20)

Exercise 6.1: Consider a pn junction like that of Fig. 6.5 with  $N_A = 10^{18}$  cm<sup>-3</sup> and  $N_D = 10^{16}$  cm<sup>-3</sup>. At room temperature, calculate a) the built-in potential of this junction, b) the extent of the depletion region on the p-side, c) the extent of the depletion region on the n-side, and d) the magnitude of the electric field at the metallurgical junction.

a) To calculate the built-in potential, we use Eq. 6.2:

$$\phi_{bi} = \frac{kT}{q} \ln \frac{N_D N_A}{n_i^2} = 0.026 \ V \ln \frac{10^{18} \ cm^{-3} \times 10^{16} \ cm^{-3}}{(1.1 \times 10^{10} \ cm^{-3})^2} = 0.84 \ V$$

b) The extent of the depletion region on the p-side is given by Eq. 6.18:

$$x_p = \sqrt{\frac{2\epsilon N_D \phi_{bi}}{qN_A(N_D + N_A)}} = \sqrt{\frac{2 \times 11.7 \times 8.85 \times 10^{-14} \ F/cm \times 10^{16} \ cm^{-3} \times 0.84 \ V}{1.6 \times 10^{-19} \ C \times 10^{18} \ cm^{-3} (10^{16} + 10^{18} \ cm^{-3})}} = 3.3 \ nm$$

c) To obtain the extent of the depletion region on the n-side, the easiest is to use the charge neutrality condition of Eq. 6.15:

$$x_n = x_p \frac{N_A}{N_D} = 3.3 \ nm \frac{10^{18} \ cm^{-3}}{10^{16} \ cm^{-3}} = 0.33 \ \mu m$$

d) The electric field at the metallurgical junction can be obtained from Eq. 6.20 but is faster to use Eq. 6.8 or Eq. 6.9 at x = 0:

$$|\mathcal{E}_{max}| = \frac{qN_D}{\epsilon} x_n = \frac{1.6 \times 10^{-19}~C \times 10^{16}~cm^{-3} \times 3.3 \times 10^{-5}~cm}{11.7 \times 8.85 \times 10^{-14}~F/cm} = 5.1 \times 10^4~V/cm$$

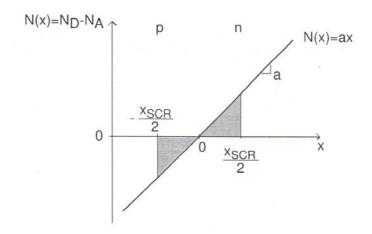

It is interesting to examine the electrostatics of the junction as a function of the relative doping level on both sides. If  $N_A = N_D$ , Eq. 6.15 implies that  $x_p = x_n$ . If  $N_A > N_D$ , then  $x_p < x_n$ , and vice versa. Notice that in this instance, Eqs. 6.11 and 6.14 indicate that  $|\phi_o(-x_p)| < \phi_o(x_n)$ . In other words, as the doping level becomes more asymmetric, the depletion region extends preferentially over the lowly-doped side and most of the electrostatic potential build up occurs there.

In practical devices, it is very common to have very asymmetric junctions in which one side is much more heavily doped than the other. For example, in a  $p^+ - n$  junction,  $N_A \gg N_D$ . In a case like this, Eqs. 6.17-6.19 imply that:

$$x_n \simeq x_{SCR} \simeq \sqrt{\frac{2\epsilon\phi_{bi}}{qN_D}} \gg x_p$$

(6.21)

The space-charge region is essentially confined to the lowly doped region and its thickness is basically determined by the doping level on the lowly doped side. As a consequence of this, the maximum electric field is given by:

$$|\mathcal{E}_{o,max}| \simeq \sqrt{\frac{2qN_D\phi_{bi}}{\epsilon}}$$

(6.22)

327

Figure 6.6: Electrostatics of a  $p^+$ -n junction in thermal equilibrium. From top to bottom: volume charge density, electric field, electrostatic potential, and energy band diagram.

and is also determined by the doping level on the lowly doped side alone. Additionally, the electrostatic potential drops mainly on the lowly doped side. From Eqs. 6.11 and 6.14, we find that:

$$\phi_o(x_n) \simeq \phi_{bi} \gg |\phi_o(-x_p)| \tag{6.23}$$

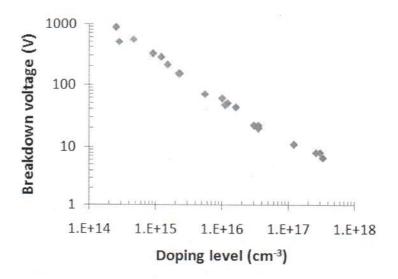

This situation is depicted in Fig. 6.6. In an asymmetric junction, the lowly-doped side dominates the electrostatics. As the doping level of the lowly-doped side increases,  $x_{SCR} \downarrow$  but  $|\mathcal{E}_{o,max}| \uparrow$ . There are important consequences associated with this that we will discuss later on.

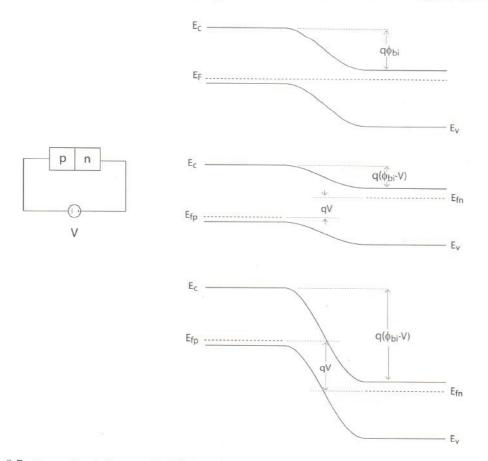

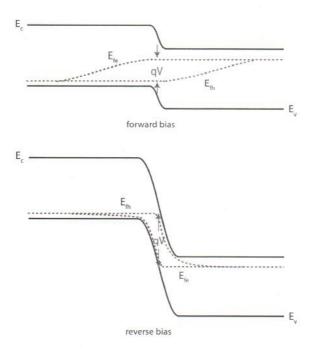

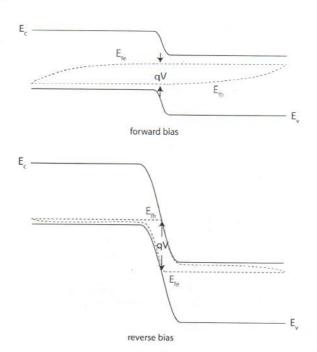

Figure 6.7: Energy band diagram of a PN junction in equilibrium (top), forward bias (middle) and reverse bias (bottom). Only the majority quasi-Fermi levels in the QNR's are drawn.

## 6.3 Current-voltage characteristics of the ideal PN diode

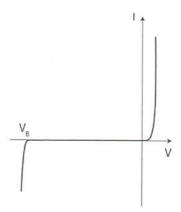

A PN diode displays rectifying behavior. With a forward bias across (p-side positive with respect to the n-side), current readily flows. Under reverse bias, only a trickle current flows and the device can be considered essentially an open circuit. This section explain this behavior of the PN diode and builds models for its current-voltage characteristics. We start by examining the modifications to the electrostatics that follows the application of a voltage.

#### 6.3.1 Electrostatics under bias

Applying a voltage across the two terminals of a PN junction modifies the electrostatics under equilibrium that we described in the previous section. In a first pass analysis, it is easier to understand the impact of a voltage by initially neglecting any influence of the current that flows. We can later on apply appropriate corrections to this simple analysis.

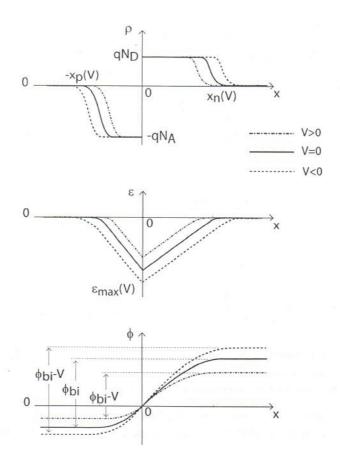

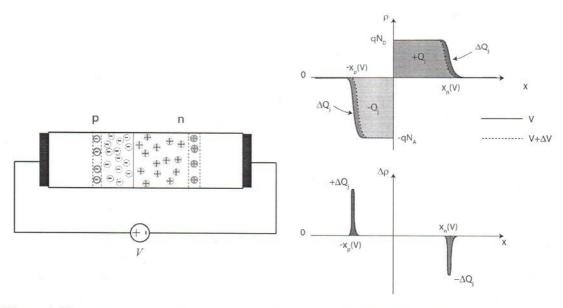

Figure 6.8: Volume charge density, electric field and electrostatic potential of a PN junction as a function of bias.

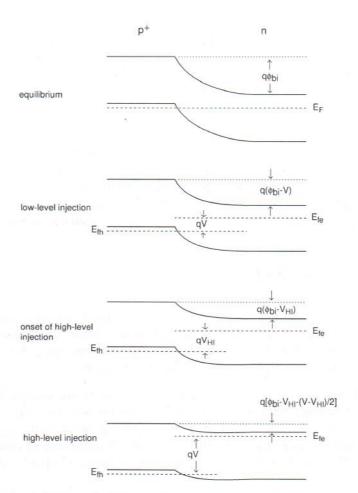

As we will see in Chapter 7, the ohmic contacts of the diode provide a way for the terminals of the battery to grab on the majority carrier Fermi levels on either side of the junction. This means that in forward bias, for example, the quasi-Fermi level for electrons on the n side is raised with respect to the quasi-Fermi level for holes on the p side by an energy difference qV, where V is the voltage of the battery. The contrary happens in reverse bias. Since the quasi-neutral regions contain lots of majority carriers, their concentrations are hard to upset in a significant way. In consequence, as the majority quasi-Fermi levels split, the entire band diagram on each side is dragged along with them. In each QNR, the bands remain flat reflecting our assumption that if no current flows, no ohmic drop occurs in the QNR's. This is illustrated in Fig. 6.7. In this figure, only the majority quasi-Fermi levels in the QNR's are drawn. The rest of the diagram has to wait until we have had a chance to discuss the physics of the current.

As a consequence of applying a voltage, the total potential difference across the junction is upset from its equilibrium value  $\phi_{bi}$ . In forward bias, it is reduced to  $\phi_{bi} - V$ . In reverse bias, it is increased to  $\phi_{bi} - V$  (in reverse bias V is negative). This in turn demands that the dipole

of charge that appears across the junction be modified too. In forward bias it has to be reduced, in reverse bias it has to be increased. Since the doping levels cannot be changed, the only way to accomplish this is to change the thickness of the SCR. The changes of the electrostatics of the PN junction upon the application of a bias are summarized in Fig. 6.8.

Qualitatively, the electrostatics of the PN junction under bias do not differ from the thermal equilibrium situation. All the equations that we have derived above basically apply in forward and reverse bias if we substitute  $\phi_{bi}$  by  $\phi_{bi} - V$ . In particular, the extent of the space-charge region becomes:

$$x_{SCR}(V) = \sqrt{\frac{2\epsilon(N_D + N_A)(\phi_{bi} - V)}{qN_A N_D}} = x_{SCR}(V = 0)\sqrt{1 - \frac{V}{\phi_{bi}}}$$

(6.24)

The maximum electric field is:

$$|\mathcal{E}_{max}(V)| = \sqrt{\frac{2qN_AN_D(\phi_{bi} - V)}{\epsilon(N_D + N_A)}} = |\mathcal{E}_{max}(V = 0)|\sqrt{1 - \frac{V}{\phi_{bi}}}$$

(6.25)

both valid in forward and reverse bias. With the application of a forward bias, the space-charge region shrinks and the maximum field decreases. A reverse bias produces the contrary effect, the SCR widens and the maximum field increases in magnitude.

If the junction is asymmetric, most of the voltage that is applied drops on the lowly doped side of the junction. The space-charge region widens preferentially into the lowly doped side.

#### 6.3.2 I-V characteristics: qualitative discussion

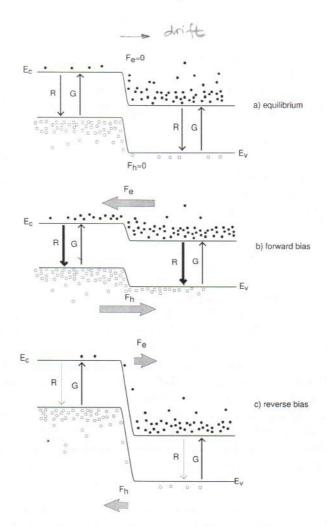

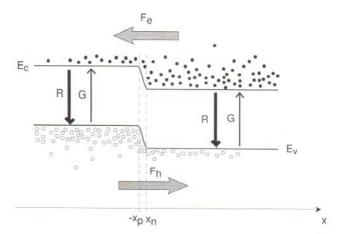

A PN junction is a *minority-carrier device*. It is the behavior of the minority carriers that represents the bottleneck to current flow. Let us first discuss this qualitatively.

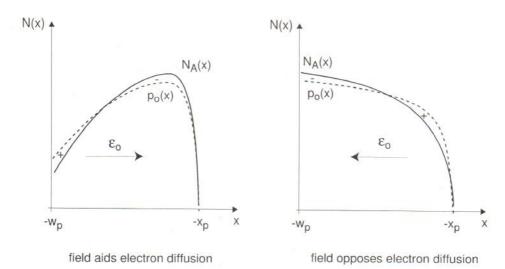

In thermal equilibrium, the net current everywhere along the diode is zero. Actually, the principle of detailed balance demands that separately, the hole and electron currents be zero at all locations. In general, carrier current is composed of drift and diffusion. In the QNR's, the carrier concentration is uniform and there is no field, so both drift and diffusion are zero separately. Inside the SCR, there is an electric field and the gradients of carrier concentrations are very steep. Here, drift has to balance diffusion precisely at every point for thermal equilibrium to hold. That means that the diffusion tendency of carriers is precisely counterbalanced by their drift inside the electric field. It is important to notice that the sign of the electric field is the correct one for this to happen.

The application of a voltage breaks this dynamic balance inside the SCR. This can be seen in Fig. 6.9. A forward bias reduces the electric field which produces a decrease in the drift component of the carrier current. In consequence, diffusion prevails over drift and there is a net electron flow from the n-side (where they are majority carriers) to the p-side (where they are

Figure 6.9: Current balance across SCR in thermal equilibrium (top), forward bias (middle), and reverse bias (bottom). In equilibrium, there is no net current crossing the SCR. In forward bias, minority carrier injection and recombination into the QNR's takes place. In reverse bias, minority carrier generation and extraction out of the QNR's dominates.

minority carriers). Similarly, holes flow from the p-side to the n-side. The term that is used to describe this process is *minority carrier injection*.

In reverse bias, the contrary happens. A negative voltage increases the electric field inside the SCR with the consequence that drift prevails over diffusion. As a result, electrons preferentially flow from the p-region (where they are minority carriers) to the n-region (where they are majority carriers). Similarly, holes flow from the n-region to the p-region. This receives the name of minority carrier extraction.

The energy view provides an intuitive picture of what happens under bias, as sketched in Fig. 6.9. In thermal equilibrium electrons are in equilibrium among themselves across the whole diode. There are many more electrons on the n-side than on the p-side. However, there is a steep energy barrier (of a height  $q\phi_{bi}$ ) separating these two regions. Some electrons on the

n-side do have enough energy to get injected into the p-region. But this is precisely balanced out by electrons on the p-side "falling down" or getting extracted into the n-region. The net flow of electrons is precisely zero in thermal equilibrium. In forward bias, this energy barrier is reduced. In consequence, many more electrons on the n-region now have enough energy to overcome the reduced barrier and get injected to the p-side. Electron extraction, on the other hand, is diminished because the electric field inside the SCR has been reduced. Conversely, in reverse bias, the barrier is increased, and, relative to equilibrium, a smaller number of electrons have enough energy to overcome the barrier and get injected into the p-side. Electron extraction from the p-side to the n-side is also increased, since the electric field inside the SCR is of a higher magnitude. A similar series of events is experienced by the holes.

But this cannot be the entire picture. What happens to the electrons injected into the p-side? How about the holes injected into the n-side? We see net current flowing through the SCR, but how is this current supported through the quasi-neutral regions?

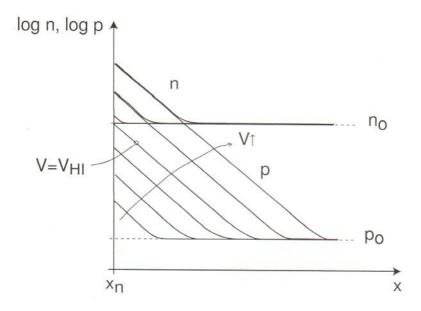

Under forward bias, minority carrier injection raises the total minority carrier concentration above the equilibrium value in the QNRs. The presence of excess minority carriers drives up the recombination rate above the value that balances the thermal generation rate. The resulting net recombination extinguishes all the injected minority carriers and makes room for more to be injected. There is then a continuous carrier flow from the majority carrier side to the minority carrier side where they recombine. Most of the recombination takes place within a few diffusion lengths of the junction where the injection takes place. Hence, at sufficient distance from the edge of the SCR, the minority carrier concentration returns to the equilibrium value. The resulting minority carrier profile is sketched at the top of Fig. 6.10. Since the supply of majority carriers in the QNR is virtually inexhaustible (and is being replenished anyway by the ohmic contact) it is the dynamics of minority carrier flow that controls the magnitude of the current. It is because of this that the PN junction is said to be a minority-carrier device.

In reverse bias, minority carrier extraction is the net consequence of drift dominating over diffusion in the SCR. The minority carrier concentrations, consequently, drop in both QNRs below their equilibrium values. This breaks again the balance between thermal generation and recombination with net generation taking place to supply the minority carriers that are extracted. A few diffusion lengths away from the edge of the SCR, the minority carrier concentrations return to the equilibrium values. The resulting carrier profiles are sketched at the bottom of Fig. 6.10. A continuous current path is established with the generated minority carriers in the QNR's being extracted by the SCR and coming out the ohmic contact to the outside world.

Does our qualitative understanding explain the rectifying characteristics of the PN junction? Surely. Let us just focus on electrons. In forward bias, the minority carrier current is proportional to the number of electrons that have enough energy to overcome the energy barrier. Since this barrier is reduced as  $\sim -V$ , the number of electrons with enough energy to overcome it goes as  $\sim e^{qV/kT}$ , and so does the current. In reverse bias, once the barrier is made large enough, electron injection from the n-side to the p-side is completely suppressed. The current is then entirely supported by electron generation in the p-QNR. This reaches its maximum value when the electron concentration drops to zero. The electron generation rate cannot increase any further beyond that and the current saturates.

Figure 6.10: Sketch of carrier profiles across pn diode in forward bias (red lines, top) and reverse bias (blue lines, bottom). In both cases the black lines represent the equilibrium carrier concentrations.

#### 6.3.3 I-V characteristics: quantitative models

Armed with the understanding produced in the previous section, we can now lay out a strategy for developing a model for the current through the PN junction. We must focus our work on the minority carriers in each quasi-neutral region (in the ideal PN diode, we neglect minority carrier generation and recombination in the SCR; we will add this later in Sec. 6.6.2). The calculation is basically a four-step process. First, we must calculate how many minority carriers are present at the respective edge of the QNR,  $n(-x_p)$  and  $p(x_n)$  (see Fig. 6.11). Second, we must derive expressions for the velocity at which minority carriers are injected into or extracted from the QNR's,  $v_e(-x_p)$  and  $v_h(x_n)$ . Third, we compute the current that minority carriers support in their flow across the SCR,  $J_e(-x_p)$  and  $J_h(x_n)$ . Finally, we add the contributions of electrons and holes and multiply by the area of the junction.

Let us start with the minority carrier boundary conditions across the SCR. These can be

Figure 6.11: Sketch of carrier flux across PN junction in forward bias indicating the edges of the SCR where current calculations are performed.

derived in various ways. An approach is to focus on the balance between drift and diffusion currents inside the SCR. In thermal equilibrium, this balance is perfect at every point in the SCR and  $J_e = J_h = 0$ . As argued above, out of equilibrium this balance is broken inside the SCR and  $J_e \neq 0$  and  $J_h \neq 0$ . The difference between drift and diffusion currents results in a net current for each type of carrier. If we were to estimate how far out of balance drift and diffusion get inside the SCR for typical diode operation, we will find (see Problem 6.13) that it is actually very little. Relative to their magnitude, drift and diffusion never get to differ very much inside the SCR of a PN diode under bias. Only a relatively small perturbation is required to support the current that originates on the generation or recombination of minority carriers in the QNR's.

The realization of this has a very important and practical consequence that we can exploit here. In Section 4.5.2 we learned that in thermal equilibrium, there is a relationship between the ratio of the carrier concentrations at two points and the difference of the electrostatic potential between those two same points. This is the Boltzmann relation. Eq. 4.58 captures this in its most general form for electrons. Across the SCR of a PN diode, the Boltzmann relation can be written, for electrons and holes, as:

$$\phi_o(x_n) - \phi_o(-x_p) = \phi_{bi} = \frac{kT}{q} \ln \frac{n_o(x_n)}{n_o(-x_p)}$$

$$\phi_o(x_n) - \phi_o(-x_p) = \phi_{bi} = -\frac{kT}{q} \ln \frac{p_o(x_n)}{p_o(-x_p)}$$

Under bias, strictly speaking these equations do not apply. However, since for each carrier type, the net carrier current is much smaller than its drift and diffusion components, then in the scale of these currents,  $J_e \simeq 0$ , and  $J_h \simeq 0$ . Hence, to first order, the Boltzmann relations should be reasonably accurate across the SCR. They can be written in the following form:

J. A. del Alamo

$$\phi_{bi} - V \simeq \frac{kT}{q} \ln \frac{n(x_n)}{n(-x_n)} \tag{6.26}$$

$$\phi_{bi} - V \simeq -\frac{kT}{q} \ln \frac{p(x_n)}{p(-x_p)}$$

(6.27)

If low-level injection conditions prevail on both sides,  $n(x_n) \simeq N_D$  and  $p(-x_p) \simeq N_A$  (see a discussion of the impact of high-level injection on Section 6.6.6). Using Eq. 6.2 and solving for the carrier concentrations on the minority carrier side, we get:

$$n(-x_p) \simeq \frac{n_i^2}{N_A} \exp \frac{qV}{kT} \tag{6.28}$$

$$p(x_n) \simeq \frac{n_i^2}{N_D} \exp \frac{qV}{kT} \tag{6.29}$$

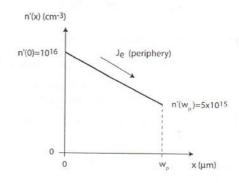

The excess carrier concentrations (defined in Eq. 3.44 and 3.45) are:

$$n'(-x_p) \simeq \frac{n_i^2}{N_A} (\exp \frac{qV}{kT} - 1)$$

(6.30)

$$p'(x_n) \simeq \frac{n_i^2}{N_D} (\exp \frac{qV}{kT} - 1) \tag{6.31}$$

These boundary conditions have all the features that we have qualitatively discussed earlier. For electrons, for example, for V = 0,  $n'(-x_p) = 0$ . If  $V \gg kT/q$ , then  $n'(-x_p) \gg n_i^2/N_A$  and grows exponentially with V. If, on the other hand,  $V \ll -kT/q$ , then  $n'(-x_p)$  saturates to  $\simeq -n_i^2/N_A$ . With the derivation of the minority carrier boundary conditions, the first step of the diode current computation is complete.

Exercise 6.2: Consider a pn junction identical to that of Exercise 6.1. At room temperature and with an applied forward bias of V = 0.6 V, calculate: a) the potential difference between the n-side and the p-side; b) the excess minority carrier concentration at the edges of the depletion region.

a) In Exercise 6.2, we computed the potential difference between the n-side and the p-side of this junction in thermal equilibrium. We found this to be  $\phi_{bi} = 0.84 \ V$ . Under forward bias, this potential difference is reduced by an amount equal to the applied voltage. Hence, we have:

$$\phi(x_n) - \phi(-x_p) = \phi_{bi} - V = 0.84 - 0.6 = 0.24 V$$

b) The excess electron concentration at the edge of the depletion region on the p-type side can be obtained from Eq. 6.30:

$$n'(-x_p) \simeq \frac{n_i^2}{N_A} (\exp \frac{qV}{kT} - 1) = \frac{1.1 \times 10^{20} \ cm^{-6}}{10^{18} \ cm^{-3}} (\exp \frac{0.6}{0.0259} - 1) = 1.3 \times 10^{12} \ cm^{-3}$$

The excess hole concentration at the edge of the depletion region on the n-tpe side can be obtained from the combination of Eqs. 6.30 and 6.31:

$$p'(x_n) = \frac{N_A}{N_D} n'(-x_p) = \frac{10^{18}~cm^{-3}}{10^{16}~cm^{-3}} 1.3 \times 10^{12}~cm^{-3} = 1.3 \times 10^{14}~cm^{-3}$$

In both cases, the excess minority carrier concentrations are much smaller than the corresponding doping levels. We can then conclude that this diode, under these conditions, is in low-level injection.

Let us now focus on the second step, the calculation of the velocity at which minority carriers are injected or extracted into or out of the QNRs. Fortunately, we have already done all the work in Ch. 5. In that chapter, we studied minority carrier flow in several quasi-neutral low-level injection situations. In particular, we studied carrier flow in semiconductor bars illuminated by a thin beam of light that produced a sheet of carrier generation. Among other things, we calculated the velocity at which minority carriers diffuse away from the generation point.

Our problem here shares a lot with those already studied in Ch. 5. In a PN junction in forward bias, the reduction of potential barrier across the SCR results in minority carrier injection into the QNRs. Once inside the QNR, the behavior of the minority carriers is identical to that of the illuminated bar. In particular, if the boundary conditions are similar, the velocity at which minority carriers diffuse into the QNR should be identical to that of photogenerated carriers.

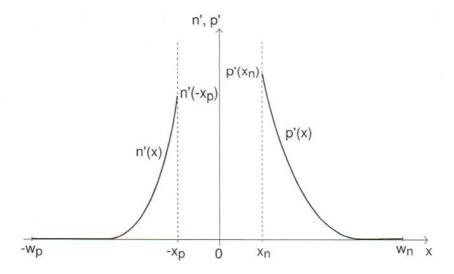

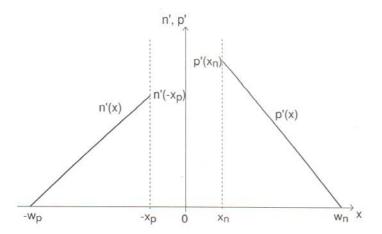

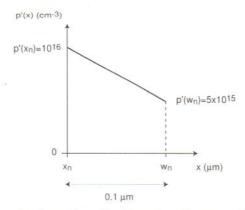

Here we are studying a "long" diode in which the QNRs are much longer than the respective minority carrier diffusion lengths. In Section 5.6.1 we found that the excess minority carrier profile in a long bar follows an exponential decay in space where the minority carrier diffusion length was the characteristic length of the exponential. We expect similar excess carrier profiles in the QNR's in the long diode, as sketched in Fig. 6.12. These profiles then follow the following analytical relations:

$$n'(x) = n'(-x_p) \exp \frac{x + x_p}{L_e} \qquad \text{in p-QNR: } x \le -x_p$$

$$p'(x) = p'(x_n) \exp \frac{-x + x_n}{L_h} \qquad \text{in n-QNR: } x \ge x_n$$

$$(6.32)$$

$$p'(x) = p'(x_n) \exp \frac{-x + x_n}{L_h} \quad \text{in n-QNR: } x \ge x_n$$

(6.33)

J. A. del Alamo 337

Figure 6.12: Excess minority carrier profiles in quasi-neutral regions of "long" diode under forward bias.

Also in 5.6.1 we found that the velocity at which photogenerated holes diffuse away from the generation point in a long n-type bar was given by  $v_h^{diff} = D_h/L_h$  (Eq. 5.69). This result also applies to the PN junction. The velocity at which minority carriers diffuse into the QNRs from their respective edges is then given by:

$$v_e^{diff}(-x_p) = -\frac{D_e}{L_e}$$

$$v_h^{diff}(x_n) = \frac{D_h}{L_h}$$

(6.34)

$$v_h^{diff}(x_n) = \frac{D_h}{L_h} (6.35)$$

where  $D_e$  and  $L_e$  pertain to minority carrier electrons in the p-type region, and  $D_h$  and  $L_h$  are associated with minority carrier holes in the n-type region. This is the result that we were looking for in step 2 of our calculation of the PN-diode current.

Step 3 consists of computing the minority carrier current injected into each QNR. Since we have both the minority carrier concentrations and the carrier velocities at the edges of the QNRs, we simply use the general results given by Eqs. 4.18 and 4.20. We get, respectively.

$$J_e(-x_p) \simeq -q v_e^{diff}(-x_p) n'(-x_p) = q \frac{n_i^2}{N_A} \frac{D_e}{L_e} \left(\exp \frac{qV}{kT} - 1\right) = J_{es}(\exp \frac{qV}{kT} - 1)$$

(6.36)

$$J_h(x_n) \simeq q v_h^{diff}(x_n) p'(x_n) = q \frac{n_i^2}{N_D} \frac{D_h}{L_h} \left( \exp \frac{qV}{kT} - 1 \right) = J_{hs} \left( \exp \frac{qV}{kT} - 1 \right)$$

(6.37)

where, for convenience, we have defined  $J_{es}$  and  $J_{hs}$  as the pre-exponential factors.

The total current density through the junction, step 4, is the sum of these two current densities. This is consistent with our assumption that no carriers recombine inside the SCR. Adding Eqs. 6.36 and 6.37, we get:

$$J = (J_{es} + J_{hs})(\exp\frac{qV}{kT} - 1)$$

(6.38)

Denoting the preexponential factor as the saturation current density,  $J_s$ , we can rewrite 6.38 as:

$$J = J_s(\exp\frac{qV}{kT} - 1) \tag{6.39}$$

which exhibits a classical rectifying behavior.

J. A. del Alamo

Exercise 6.3: Consider a pn diode identical to that of Exercises 6.1 and 6.2. Now consider that the p- and n-regions are "long" from the minority carrier point of view. At room temperature and with an applied forward bias of V = 0.6 V, estimate the current density flowing through this diode.

To estimate the diode current density we need to separately compute the current density injected into each quasi-neutral region and add them up. In Exercise 6.2, we already computed the excess minority carrier concentrations at the edges of the depletion region under the same conditions as given here. The best way to proceed is then to estimate the velocity at which excess carriers are injected into each QNR using Eqs. 6.34 and 6.35. For this, we need to know the respective diffusion coefficients and diffusion lengths.

To estimate the diffusion coefficients, we can use the mobility data graphed in Fig. 4.3 or the corresponding fits given in Appendix E. For electrons in the p-type region, we obtain  $\mu_e = 344 \ cm^2/V.s$  and  $D_e = 9.0 \ cm^2/s$ . For holes in the n-type region, we obtain  $\mu_h = 476 \ cm^2/V.s$  and  $D_h = 12.4 \ cm^2/s$ .

To estimate the diffusion lengths, we can either use Fig. 5.17 or we can obtain the corresponding minority carrier lifetimes and then use Eq. 5.54 to obtain the diffusion length. We proceed this way. From Appendix E, we estimate the minority carrier lifetime in the p-type region as  $\tau_e = 2.3 \times 10^{-6}$  s and in the n-type region as  $\tau_h = 1.3 \times 10^{-4}$  s. This yields diffusion lengths that are  $L_e = 4.6 \times 10^{-3}$  cm and  $L_h = 4.0 \times 10^{-2}$  cm, respectively.

Now, using Eqs. 6.34 and 6.35 we estimate the velocity at which minority carriers are injected into each QNR. For electron injection into the p-QNR, we have:

$$|v_e^{diff}(-x_p)| = \frac{D_e}{L_e} = \frac{9.0 \text{ cm}^2/s}{4.6 \times 10^{-3} \text{ cm}} = 2.9 \times 10^3 \text{ cm/s}$$

For hole injection into the n-QNR, we have:

$$v_h^{diff}(x_n) = \frac{D_h}{L_h} = \frac{12.4 \text{ cm}^2/\text{s}}{4.0 \times 10^{-2} \text{ cm}} = 3.1 \times 10^2 \text{ cm/s}$$

The current density injected into each QNR can be obtained using Eqs. 6.36 and 6.37. For the p-QNR, we have:

$$J_e(-x_p) = q |v_e^{diff}(-x_p)| n'(-x_p) = 1.6 \times 10^{-19} C \times 2.9 \times 10^3 cm/s \times 1.3 \times 10^{12} cm^{-3}$$

=  $6.0 \times 10^{-4} A/cm^2$

Similarly, for the n-QNR:

$$J_h(x_n) = q v_h^{diff}(x_n) p'(x_n) = 1.6 \times 10^{-19} C \times 3.1 \times 10^2 cm/s \times 1.3 \times 10^{14} cm^{-3}$$

$$= 6.5 \times 10^{-3} A/cm^2$$

The total diode current density is the sum of these two components:

$$J = J_e(-x_p) + J_h(x_n) = 7.1 \times 10^{-3} \ A/cm^2$$

If the junction has an area A, the currents injected into the p- and n-regions are respectively given by:

Figure 6.13: Sketch of I-V characteristics of ideal PN junction in linear and semilogarithmic scales.

$$I_p = AJ_e(-x_p) = AJ_{es}(\exp\frac{qV}{kT} - 1)$$

(6.40)

$$I_n = AJ_h(x_n) = AJ_{hs}(\exp\frac{qV}{kT} - 1)$$

(6.41)

and the total current is:

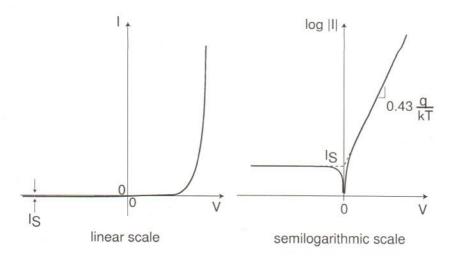

$$I = I_p + I_n = I_s(\exp\frac{qV}{kT} - 1)$$

(6.42)

with  $I_s = AJ_s$ .  $I_s$  is known as the diode saturation current.

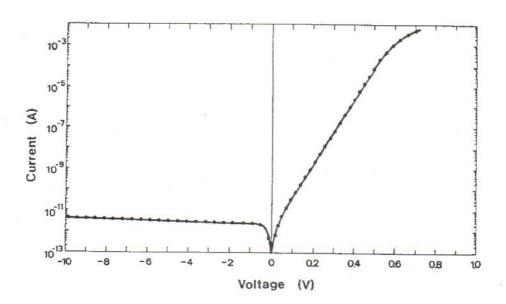

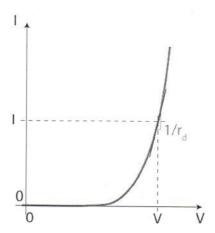

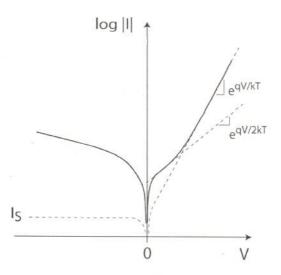

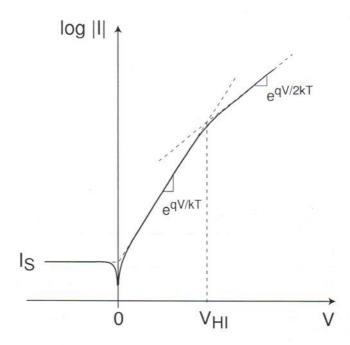

Eq. 6.42 is the result that we were looking for. It gives the current through the diode as a function of the applied voltage. It is all in terms of physically meaningful parameters and fundamental constants. In forward bias, the current grows exponentially, as we expected. In reverse bias, the current saturates to  $-I_S$ , also as expected. This behavior is plotted in Fig. 6.13. Since  $I_S$  tends to be small, it is common to graph the I-V characteristics in a semilogarithmic scale, as shown on the right of Fig. 7.14. In a semilog scale, the forward bias current appears as a straight line with a slope of  $(q/kT)\log e = 0.43q/kT$ , which only depends on temperature. The higher the temperature, the lower the slope. It is common to refer to this slope in units of mV/dec, that is, the voltage required (in mV) to produce an increase in current of a factor of ten. At room temperature, this figure is  $60 \ mV/dec$ , a handy number to remember.

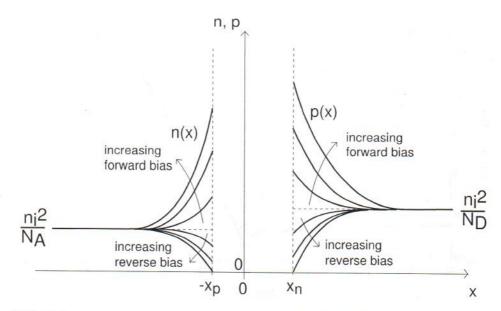

Since the boundary conditions 6.30 and 6.31 capture both forward and reverse bias and the profiles 6.32 and 6.33 are valid in both forward and reverse bias, the equations that we have derived for the I-V characteristics, Eq. 6.38-6.42 apply in both forward and reverse bias.

Before we proceed further, it is of value to examine the relative magnitude of the two terms of

Figure 6.14: Evolution of minority carrier profiles in the quasi-neutral regions of a "long" diode as a function of bias.

the diode current that arise from each of the diode regions. If the doping levels are similar, these two terms are of comparable order of magnitude. The diffusion velocity for electrons is higher than that of holes so, for identical doping levels, the electron injection in the p-type region is somehow higher than hole injection into the n-type region. However, the current is inversely proportional to the doping level. So, in an asymmetric junction, current injection into the lowly-doped region tends to dominate.

It is important to emphasize here that the rectifying behavior of the diode is entirely due to the boundary condition at the edges of the SCR. This is clearly seen in the sketch of the minority carrier profiles as a function of bias shown in Fig. 6.14. In forward bias, the higher the voltage, the higher the concentration of minority carriers that are injected and contribute to current via their recombination with majority carriers. The relationship is of a Boltzmann type. In reverse bias, our model predicts that the minority carrier concentrations at the edges of the SCR drop to negligible values when  $|V| \gg kT/q$ . Since the minority carrier concentrations cannot be any smaller than zero, that means that when  $|V| \gg kT/q$ , the generation rate everywhere in the QNRs saturates and the reverse current also saturates. The reverse current is  $-I_s$  and it is usually a very small value (typically  $I_s \sim 1~pA/cm^2$  in Si PN junctions at room temperature).

Several key dependencies are observed in Eq. 6.42. First of all, in forward bias, the current increases exponentially with V. If plotted in a semilogarithmic scale, as sketched in Fig. 6.13, the forward characteristics appear as a straight line with a slope of 0.43q/kT. It actually is common in the literature to refer to the inverse of this slope, whose ideal value at room temperature is

<sup>&</sup>lt;sup>1</sup>Obviously, the carrier concentration cannot drop to zero as it would not be possible to support a finite current this way. This is a limit of this simplified formulation. In reality, the carrier concentrations at the edges of the SCR drop to very small values that are largely bias insensitive. This produces current saturation.

Figure 6.15: Experimental I-V characteristics of Si PN junction at room temperature [Ref?].

Figure 6.16: Normalized experimental I-V characteristics of Si PN junction at several temperatures [adapted from P. Cappelletti et al., J. Appl. Phys. 57, 646, (1985)].

Figure 6.17: Sketch of current profiles across PN diode in forward bias.

60 mV/decade. The extrapolation of this straight line to V=0 is  $I_s$ . This is also the magnitude of the current at a sufficient reverse bias.

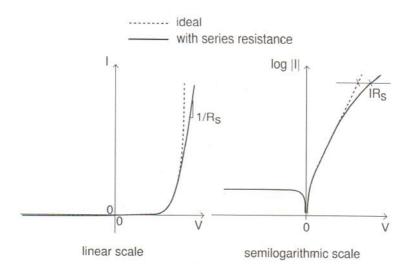

These key features are actually seen in experimental PN junctions. Fig. 6.15 shows a semilogarithmic plot of the I-V characteristics of a PN diode at room temperature. These characteristics display a nearly ideal behavior. In forward bias, the current increases exponentially with a slope of about 62 mV/dec. The extrapolation of this current to V=0 V gives  $I_s\simeq 1$  pA. In reverse bias, the current is rather independent of bias and equal to about 4 pA, which is very close to  $I_s$ . The deviation from the perfect straight line at high forward bias is due to series resistance. The slight slope of the current in reverse bias is due to generation in the space-charge region. These non-idealities are discussed below.

Fig. 6.16 shows  $I/I_s$  vs. qV/kT for a PN junction at several temperatures. For all temperatures, the data follows Eq. 6.42 fairly well. Note in particular that the extrapolation of the forward and reverse characteristics meet at V=0, as predicted by simple theory.

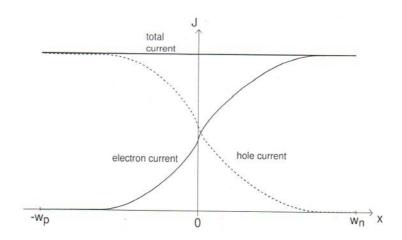

It is instructive to think about the electron and hole current profiles across the entire PN junction. They are shown in Fig. 6.17 for forward bias. A similar picture can be constructed in reverse bias. The current profiles are similar to those of the example of Section 5.6.1. The total current is the sum of the electron injected current to the p-region plus the hole-injected current to the n-region. Across the narrow space-charge region, we assume that there is negligible recombination and the currents do not change. In the quasi-neutral regions, the minority carrier currents fall off exponentially from the edge of the space-charge region. Far away from the junction, the total current is entirely supported by the majority carriers. At the end of the p region, the total current is entirely due to holes, while at the end of the n region, it is completely carried by electrons. The majority carrier currents flow through their respective ohmic contacts to the outside world.

Now that we have computed the carrier currents at all points in a PN junction, we are in a position to complete the energy band diagrams out of equilibrium by sketching the quasi-Fermi levels everywhere. This is done in Fig. 6.18 for a junction where both QNR's are much longer

Figure 6.18: Schematic energy band diagram in forward and reverse bias showing the location of the quasi-Fermi levels.

than the respective minority carrier diffusion lengths. The assumption that we made inside the SCR that the carriers are in quasi-equilibrium implies that the quasi-Fermi levels are flat there. In the QNR's, the further away we move from their edge with the SCR, the closer we are to reestablishing equilibrium. A few diffusion lengths away, in fact, the carrier concentrations recover their equilibrium values. In consequence, the minority carrier quasi-Fermi levels approach the majority carrier ones and eventually merge into one as quasi-equilibrium is obtained sufficiently far away.

There is an interesting and relevant implication of quasi-equilibrium existing for electrons and holes separately and the quasi-Fermi levels being flat across the space-charge region. In Ch. 4, we saw that the np product was exponentially dependent on the difference of the quasi-Fermi levels (see Eq. 4.91). For the SCR of a PN junction, this difference is precisely qV. As a consequence, we can write:

$$np = n_i^2 \exp \frac{qV}{kT} \tag{6.43}$$

From this equation, it is trivial to derive the boundary conditions 6.28 and 6.29.

J. A. del Alamo

Figure 6.19: Behavior of capacitor to static voltage (left) and a dynamic voltage (right). In the static situation, the current is zero. In the dynamic situation, current flows as the plates of the capacitor charge or discharge.

## 6.4 Charge-voltage characteristics of ideal PN diode

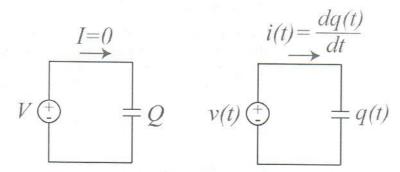

At first sight, it would seem that a formulation of the current-voltage characteristics of a diode is all we could possibly need to analyze circuits containing diodes. However, the current-voltage characteristics only provide a simple *static* description of the device. In most applications, we also care about the *dynamic* operation of the diode. In power electronics, for example, the diode voltage often changes abruptly from a large reverse bias to a forward bias and back. In many analog applications, it is common to apply to the diode a rapidly varying small-signal voltage on top of a bias. The frequency of the small-signal can be quite high. To correctly describe the operation of the diode in situations like these, we need to keep track of the charge stored inside. What does this mean?

Let us think for a moment about about a parallel plate capacitor, as sketched in Fig. 6.19. The static current-voltage characteristics of an ideal parallel plate capacitor are very simple: for any voltage, the current is zero (left in Fig. 6.19). However, the dynamic behavior of the capacitor is much more interesting (right in Fig. 6.19). When the voltage changes, current flows to charge the plates of the capacitor. For example, if the voltage on one plate rises with respect to the other, positive charge is deposited to that plate and the same amount of positive charge is removed from the other plate. This produces a flow of charge through the circuit which results in current. <sup>2</sup> The current that flows through the circuit is given by the familiar expression i(t) = dq(t)/dt, where q(t) is the charge stored in the capacitor (one plate is charged with +q while the other plate is charged with -q.) If we were to describe the behavior of the capacitor by only its static current-voltage characteristics (I = 0 for any V), we would clearly miss its interesting dynamic features!

A similar situation occurs in virtually every semiconductor device. Just like in a parallel plate capacitor, in a semiconductor device there is stored charge with a magnitude that depends on the applied voltage. If the voltage changes, the stored charge has to change and that produces a current flow. This needs to be accounted for in the analysis of circuits that contain semiconductor

<sup>&</sup>lt;sup>2</sup>In reality we know that current should be described by the retrograde movement of electrons. So, for the picture on the right of Fig. 6.19, when the voltage rises on one plate with respect to the other, electrons are taken away from the first plate and the same amount of electrons are added to the second plate.

devices. This is what the charge-voltage characteristics describe.

For the case of the PN diode, what charge is it that we need to account for? Two types, actually. One is associated with the depletion region across the metallurgical junction and the second one is associated with minority carrier injection into the quasi-neutral regions. The next two sections discuss this in more detail and derive models for these two types of stored charge.

#### 6.4.1 Depletion charge

In Sec. 6.3.1 we saw that the extent of the depletion region in a PN diode is modulated by the applied voltage. A reverse bias enlarges the depletion layer and a forward bias shrinks it. The depletion layer consists of two distinct regions: on the n side of the junction there is a region that is positively charged while on the p-side of the junction there is another region that is negatively charged. Overall charge neutrality demands that the absolute amount of charge in both regions be the same. This clearly resembles the two plates of a capacitor.

This situation is depicted in Fig. 6.20. This graph shows the charge distribution in the depletion region of a diode at a certain bias V and the change in this charge when the bias increases by a small amount  $\Delta V$ . For simplicity, let us assume that both V and  $\Delta V$  are positive, though this is not necessary. At first sight, there seems like there is a sign discrepancy in the charge with respect to the situation in a parallel plate capacitor. The positive side of the diode (the p side) has negative charge in its share of the depletion region while the negative side of the diode (the n side) has positive charge in its portion of the SCR. This is not a problem because what matters is how this charge changes when V changes. So, if V increases by an amount  $\Delta V$ , we know that the depletion region shrinks on both sides. That means that a sliver of positive charge must be deposited at the edge of the SCR on the p-side and the same amount of negative charge has to be deposited at the other edge of the SCR on the n side, as sketched in the bottom figure. The change in charge that occurs as a result of the change in voltage clearly has the right sign and current flows in the circuit with the expected sign.

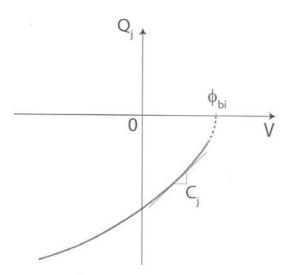

From the discussion on the electrostatics of the PN diode of Sec. 6.3.1 we can immediately write the charge on either side of the depletion region as a function of the applied voltage. For the p-side, for example:

$$Q_{j}(V) = -AqN_{A}x_{p} = -A\sqrt{\frac{2q\epsilon N_{D}N_{A}(\phi_{bi} - V)}{N_{D} + N_{A}}}$$

(6.44)

The negative sign reflects the fact that the charge on the p side is due to exposed acceptors. We obtain an identical expression with a positive sign if we evaluate the charge on the n-side of the SCR. This expression includes the area of the junction so the units of  $Q_j$  are Coulombs.

This expression can be rewritten in the following form:

$$Q_j(V) = Q_j(V=0)\sqrt{1 - \frac{V}{\phi_{bi}}}$$

(6.45)

J. A. del Alamo

Figure 6.20: Sketch of volume charge density in the SCR of a PN junction at a certain bias V and its change upon the application of an additional small voltage  $\Delta V$ .

As forward bias increases, the depletion region shrinks and  $Q_j$  is reduced in magnitude. As the reverse bias increases, on the other hand,  $Q_j$  increases in magnitude. The voltage dependence of  $Q_j$  is square root. This is sketched in Fig. 6.21. Notice how, in spite of the negative sign in  $Q_j$ , its derivative with V (the capacitance, discussed below) is positive, as it should be.

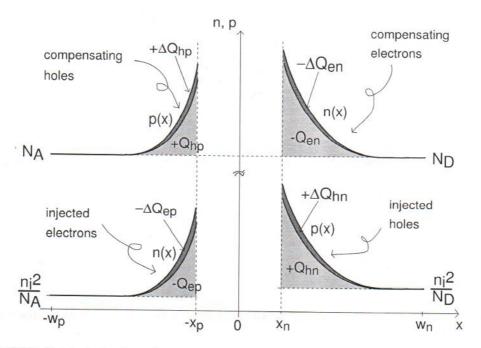

#### 6.4.2 Minority carrier charge

The second type of stored charge in a PN diode has to do with minority carrier injection. In a forward biased PN junction, the two quasi-neutral regions are flooded with excess minority carriers. Quasi-neutrality is preserved by piling up a nearly identical concentration of majority carriers at every point in space, as sketched in Fig. 6.22. The required majority carriers are easily delivered by the battery through the respective ohmic contact. As studied in detail in Chapter 5, quasi-neutrality is a consequence of the relatively high conductivity of extrinsic semiconductor regions. Even a very small electric field can produce a substantial majority carrier current in a moderately doped region. The current circulates until the majority carrier distribution matches the minority carrier profile. This occurs in a time scale of the dielectric relaxation time, a very short time.

The modification of the majority carrier concentrations relative to the doping level is very small if low-level injection conditions are maintained. The assumption of low-level injection demands in a p-type region, for example, that  $n' \ll p_o$ . Since quasi-neutrality is satisfied when  $n' \simeq p'$ , then  $p' \ll p_o$  and  $p \simeq p_o$ . Therefore, for most purposes, we can still assume that the majority carrier concentration equals the doping level everywhere.

Figure 6.21: Sketch of the charge-voltage characteristics associated with the space-charge region of a PN diode.

Now let us consider what happens to the carrier profiles if we increase the forward voltage by a small amount, as sketched in Fig. 6.22. A slightly higher forward voltage injects more minority carriers at the edge of the SCR. This results in an increased overall minority carrier concentration everywhere. The majority carrier concentration must match up also this small increase in total charge in order to preserve quasi-neutrality. We again see that the change in voltage results in a change in stored charge, just like in a capacitor.

Let us look in more detail at the n-side. If the forward voltage increases by a small amount, the p-side injects holes to the n-QNR. This results in an overall increase  $\Delta Q_{hn}$  in the positive charge stored in the n-region. In order to preserve quasi-neutrality, the ohmic contact of the n-type region delivers the same amount of electrons with a total charge  $\Delta Q_{en} = -\Delta Q_{hn} \equiv -\Delta Q_n$ . In this way, the net charge in the n-QNR is back to zero. To maintain quasi-neutrality point by point, the spatial charge distribution of additional holes matches very closely that of extra electrons, as indicated in Fig. 6.22. The additional holes injected into the n-QNR were provided by the positive side of the battery. The electrons were provided by the negative side of the battery consistent with the sign notation for a capacitor. The moment the minority carrier profile has reached its final distribution at the new forward voltage, the flow of charge bound to get stored ceases. The normal diode current continues to flow at a slightly higher value.

A similar sequence of events takes place on the p-QNR. If the forward voltage changes, the negative terminal of the battery delivers negative charge in the form of excess electrons,  $\Delta Q_{ep}$ , which is matched point by point by positive charge delivered by the positive terminal of the battery in the form of excess holes through the ohmic contact to the p-QNR, that is,  $\Delta Q_{ep} = -\Delta Q_{hp} \equiv -\Delta Q_p$ . The p-QNR also displays the same capacitive effect as the n-QNR. Furthermore, both "capacitors" are located in parallel directly across the terminals of the PN junction.

We are now in a position to develop a model for the stored charge in the n- and p-QNRs. These can be obtained simply by integrating the respective excess minority carrier concentrations:

Figure 6.22: Sketch of minority and majority carrier profiles in a PN junction in forward bias. Both sides are long in comparison with the minority carrier diffusion lengths. In response to a small change in the voltage applied to the junction, both the minority and the majority carrier concentrations change by the same amount point-by-point in the quasi-neutral regions.

$$Q_p = qA \int_{-w_p}^{-x_p} n'(x) dx \qquad (6.46)$$

$$Q_n = qA \int_{x_n}^{w_n} p'(x) dx (6.47)$$

In these expressions,  $Q_p$  refers to the stored charge in the p-type QNR and and  $Q_n$  to that of the n-type QNR.

We derived expressions for the excess carrier concentrations in the two QNRs for our ideal PN diode (Eqs. 6.32 and 6.33). Plugging these expressions in and integrating, we get:

$$Q_p = qAL_e n'(-x_p)$$

$$Q_n = qAL_h p'(x_n)$$

(6.48)

$$Q_n = qAL_h p'(x_n) (6.49)$$

We can rewrite these expressions in terms of the minority carrier current density injected into the respective regions by using Eqs. 6.36 and 6.37 on the one hand, and 6.34 and 6.35 on the other hand, to obtain:

$$Q_p = A \frac{L_e^2}{D_e} J_e(-x_p) (6.50)$$

$$Q_n = A \frac{L_h^2}{D_h} J_h(x_n) \tag{6.51}$$

Finally, using the definitions made in Eqs. 6.40 and noting that  $L^2/D$  is equal to the minority carrier lifetime, we obtain:

$$Q_p = \tau_e I_p$$

$$Q_n = \tau_h I_n$$

(6.52)

$$(6.53)$$

where  $\tau_e$  and  $\tau_h$  are, respectively, the minority carrier lifetimes for electrons in the p-region and holes in the n-region.

The total stored charge is simply, then:

$$Q_d = Q_p + Q_n = \tau_e I_p + \tau_h I_n = Q_s (\exp \frac{qV}{kT} - 1)$$

(6.54)

This expression and the individual components of the current given by Eqs. 6.52 and 6.53 make good physical sense. If we think about this in forward bias, when  $Q_d$  can become sizable, the current flowing through the diode is entirely due to recombination. For each region of the diode, the characteristic time constant of this process is the recombination lifetime  $\tau$ . Then the amount of stored charge has to be  $\tau I$ . Conversely, a charge  $\overline{Q_d}$  recombining in a time span of  $\tau$  gives rise to a current  $I = Q_d/\tau$ .

An important result obtained here is that the minority carrier charge stored in a diode goes as  $Q_d \propto \exp(qV/kT) - 1$ . This reflects the boundary conditions for excess carrier concentrations at the edges of the SCR. In forward bias, this charge increases exponentially. In reverse bias, this charge saturates to a very small value that is in most cases negligible.

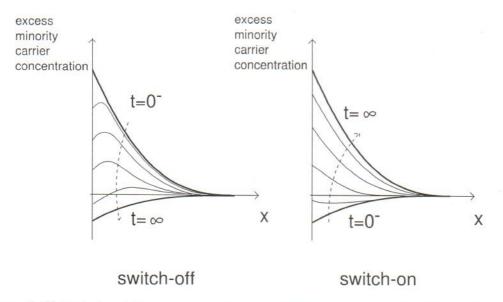

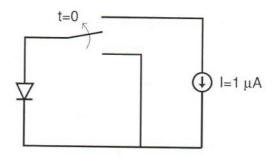

Minority carrier storage in PN diodes is an issue that affects its switching characteristics in a very significant way. It we attempt to switch a diode from a forward bias state to a reverse state, the transitory is not complete until all the minority carrier charge that exists in forward bias is disposed of. This can take substantial time. Similarly, if we try to switch a PN diode from reverse bias to forward bias, a lot of current needs to be delivered to provide the minority carrier charge that needs to be stored. This also takes time. We analyze the situation in detail in Appendix AT6.3. The absence of minority carrier storage in Schottky diodes, as we will see in Ch. 7, makes these devices preferable for switching applications.

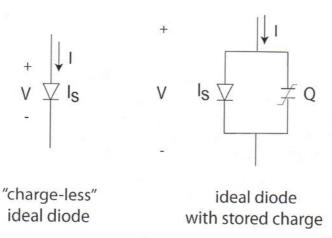

Figure 6.23: Left: symbol for charge-less ideal diode.  $I_s$  represents its saturation current. Right: large-signal equivalent circuit model of ideal diode.

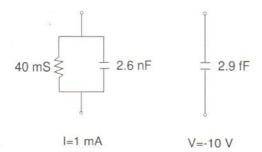

## 6.5 Equivalent circuit models of the ideal PN diode

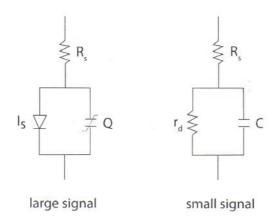

An equivalent circuit model for a semiconductor device is a circuit-like description of its behavior that uses elemental components such as resistors, capacitors, current sources, voltage sources, and others. One of these elemental components in the equivalent circuit models toolbox is actually a "charge-less" ideal diode. This is a two-terminal element that exhibits rectifying current-voltage characteristics as given by Eq. 6.42 but does not hold stored charge. It is then more akin to a non-linear resistor with rectifying characteristics. A symbol for a charge-less ideal diode is shown on the left of Fig. 6.23. A charge-less ideal diode is characterized by a single parameter, its saturation current  $I_s$  which is often written right next to the symbol. In the chapters that follow, we will use this element when constructing equivalent circuit models for the Schottky diode, the MOSFET and the bipolar junction transistor.

Our concept of ideal diode in this chapter does involve stored charge, as discussed in detail in the previous section. Therefore, to the charge-less ideal diode, we need to add a storage element in parallel. The reason for the parallel configuration is the fact that the same voltage that feeds the current through the diode also drives charge storage. This combination of elements is the most elemental equivalent circuit model for an ideal diode and is shown on the right of Fig. 6.23. The charge storage element is usually represented by a capacitor-like symbol with a characteristic broken line across, as indicated in the figure. This is to suggest that this is a non-linear element. As we now know, in an ideal diode, charge storage exhibits a complex voltage dependence given by the sum of the depletion region capacitance, Eq. 6.44, and the minority carrier charge, Eq. 6.54.

The equivalent circuit model on the right of Fig. 6.23 is referred to as a large-signal equivalent circuit. The two branches in parallel represent the direct diode current that flows upon the application of a voltage plus the current needed to charge or discharge the diode if the voltage changes. So, in a general dynamic situation, the terminal diode current is given by:

$$I = I_s(\exp\frac{qV}{kT} - 1) + \frac{dQ}{dt}$$

(6.55)

To keep the notation simple, I, V, and Q here denote instantaneous time dependent variables.

In many applications, it is also important to develop a good understanding of the small-signal behavior of semiconductor devices. This refers to their response to small excursions around its bias point. Devices are used this way in many analog and communications applications. The small-signal behavior of a device can be obtained by linearizing the current and charge equations.

For the diode, starting with the current-voltage characteristics, we apply a voltage across that consists of a bias V, plus a small signal v. The resulting current is:

$$I + i = I_s[\exp\frac{q(V+v)}{kT} - 1]$$

(6.56)

If v is small in the scale of kT/q, then we can linearize the exponential by selecting the first two terms of the Taylor series expansion:

$$I + i \simeq I_s[\exp\frac{qV}{kT}(1 + \frac{qv}{kT}) - 1] = I + \frac{q(I + I_s)}{kT}v$$

(6.57)

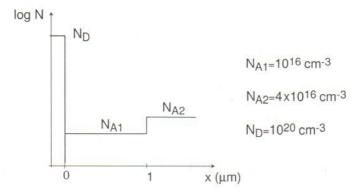

From the small-signal point of view, the ideal diode looks like a resistor of value:

$$r_d = \frac{kT}{q(I+I_s)} \tag{6.58}$$

$r_d$  is referred to as the <u>dynamic resistance</u> of the diode. Its meaning is graphically illustrated in Fig. 6.24. The dynamic resistance is the inverse slope of the I-V characteristics of the diode at the selected bias point. Its value, therefore, depends on the bias that has been selected. In forward bias, if  $V \gg kT/q$ , then:

$$r_d \simeq \frac{kT}{qI} \tag{6.59}$$

This is an important result. The dynamic resistance of a diode is inversely proportional to the diode current. The dependence is completely fundamental, that is, it is completely specified by fundamental constants and the diode temperature. For a diode biased at I=1 mA at room temperature, for example,  $r_d=26$   $\Omega$ . This fundamental relationship suggests that the value of  $r_d$  is independent of the design of the diode; a modern diode and a diode from the early days of microelectronics both present an identical dynamic resistance if biased at the same current level. Of course, this is to the extent that they both exhibit I-V characteristics that approach the ideal behavior.

We turn our attention now to the charge-voltage characteristics. It is interesting to realize that, using the chain rule, the second term in Eq. 6.55 can be written as:

Figure 6.24: Illustration of dynamic resistance of a PN diode. The dynamic resistance characterizes the slope of the I-V characteristics of the diode at a given bias point. Its value depends on the selected bias point. For small excursions of voltage around this bias point, the dynamic resistance captures reasonably well the response of the diode.

$$\frac{dQ}{dt} = \frac{dQ}{dV}\frac{dV}{dt} = C\frac{dV}{dt} \tag{6.60}$$

where C has the units of capacitance. This suggests an alternative, but completely equivalent description of charge storage in a diode (and other semiconductor devices) in terms of a diode capacitance defined as:

$$C(V) = \frac{dQ}{dV} \tag{6.61}$$

This equation is written in a way to emphasize the fact that a device capacitance is in general bias dependent.

Describing charge storage in terms of capacitance has the advantage that only the variables I and V are needed to completely specify the situation. Also, Eq. 6.60 suggests that the absolute value of Q does not matter but it is dQ/dV, or capacitance, what really counts for the dynamics of a device.

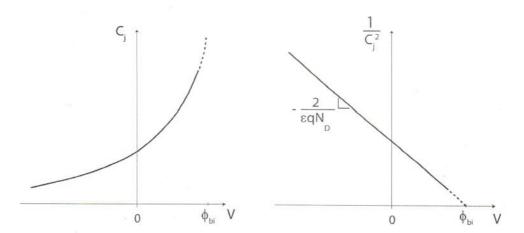

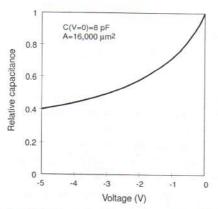

Since in a pn diode there are two components of Q, the diode capacitance also contains two terms. Associated with charge storage in the SCR there is a capacitance that is called *depletion capacitance* or *junction capacitance*,  $C_j$ . We can easily evaluate an expression for it. If we go back to Eq. 6.44, for example, and use the capacitance definition of Eq. 6.61, we immediately obtain:

$$C_j(V) = A\sqrt{\frac{\epsilon q N_A N_D}{2(N_D + N_A)(\phi_{bi} - V)}} = \frac{C_j(V = 0)}{\sqrt{1 - \frac{V}{\phi_{bi}}}}$$

(6.62)

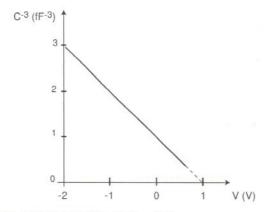

Figure 6.25: Sketch of C-V characteristics of a PN junction (left). Also plotted (right) is  $1/C^2$  vs. V for an asymmetric p<sup>+</sup>-n junction. The doping level on the lowly-doped side and the built potential can be determined from this plot.

This expression is sketched in Fig. 6.25. The shape of  $C_j$  with V makes good sense if we think of this as a parallel plate capacitor where the plates are separated by the thickness of the space-charge region, as Fig. 6.20 suggests. Starting from V=0, as forward bias is applied, the space-charge region shrinks and the capacitance increases. If reverse bias is applied, the space-charge region widens and the capacitance decreases. In fact this way of thinking yields the expression of  $C_j$  very quickly if we write:

Alternatively:

$$C_j(V) = A \frac{\epsilon}{x_{SCR}(V)} \tag{6.63}$$

Substituting  $x_{SCR}$  from Eq. 6.24 into this expression immediately yields Eq. 6.62.

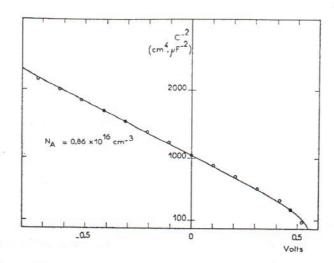

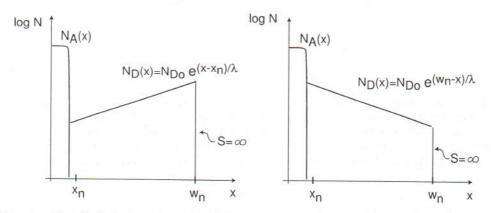

Measuring the capacitance-voltage characteristics often constitutes a powerful way to characterize semiconductor devices. We use an asymmetric  $p^+ - n$  junction to illustrate this. In this case, Eq. 6.62 reduces to:

$$C_j(V) = A\sqrt{\frac{\epsilon q N_D}{2(\phi_{bi} - V)}} \tag{6.64}$$

Here we see that the capacitance is dominated by the doping on the lowly-doped side of the junction. In fact,  $C_j(V)$  in Eq. 6.64 only depends on  $N_D$  and  $\phi_{bi}$ . So C-V measurements can easily yield these two parameters. A particularly easy way to accomplish this is to plot  $1/C_j^2$  as a function of V. From Eq. 6.64 for the p<sup>+</sup>-n junction, we find:

$$\frac{1}{C_j^2} = \frac{2(\phi_{bi} - V)}{\epsilon q N_D A^2} \tag{6.65}$$

This expression shows that  $1/C_j^2$  depends linearly on voltage with a negative slope that is a

Figure 6.26: Experimental  $1/C_j^2$  vs. V characteristics of a Si PN junction. From the slope of the straight line, the doping level on the lowly-doped side is determined [data from Fortini et al., IEEE Trans. Electron Dev. ED-29, 1604 (1982)].

function of  $N_D$ , the area of the diode and fundamental constants. Also,  $1/C^2$  goes to zero as V goes to  $\phi_{bi}$ . This behavior is sketched in Fig. 6.25. Fig. 6.26 provides an experimental demonstration of this. It is then clear that from C-V measurements, knowing the area of the diode we can determine the doping level on the lowly doped side of the diode and the built-in potential of the junction.

**Exercise 6.4**: Consider a pn diode identical to that of Exercises 6.1, 6.2 and 6.3. The diode has a junction area of 10  $\mu$ m<sup>2</sup>. Estimate the junction capacitance associated with this diode at room temperature and under an applied forward bias of V = 0.6 V.

This can be done in different ways. The fastest way is perhaps using the result of Exercise 6.1 where we estimated the extent of the SCR in this diode under zero bias. There we found that  $x_{SCR} \simeq x_n = 0.33 \ \mu m$ . The junction capacitance at zero bias is then:

$$C_j(V=0) = A \frac{\epsilon}{x_{SCR}(V=0)} = 10 \times 10^{-8} \ cm^2 \times \frac{1.0 \times 10^{-12} F/cm}{0.33 \times 10^{-4} \ cm} = 3.1 \times 10^{-15} \ F = 3.1 \ fF$$

The junction capacitance at a certain voltage can be obtained using Eq. 6.62:

$$C_j(V) = \frac{C_j(V=0)}{\sqrt{1 - \frac{V}{\phi_{bi}}}} = \frac{3.1 \ fF}{\sqrt{1 - \frac{0.6}{0.84}}} = 5.8 \ fF$$

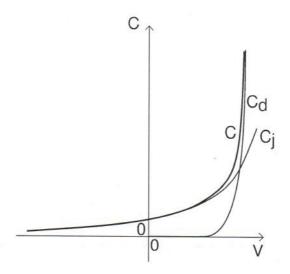

The second source of stored charge in a diode is minority carrier charge. This can be described through a capacitance that is called the **diffusion capacitance**. We can obtain an expression for this by using Eq. 6.54 in Eq. 6.61:

$$C_d = \frac{dQ_d}{dV} = \frac{q}{kT} Q_s \exp \frac{qV}{kT}$$

(6.66)

The voltage dependence of  $C_d$  is a pure exponential.  $C_d$  goes to zero for reverse bias and increases exponentially with forward bias. If the forward bias voltage exceeds kT/q, then we can approximate  $C_d$  with:

$$C_d \simeq \frac{q}{kT}Q_d \tag{6.67}$$

or simply, q/kT times the total stored minority carrier charge in the diode.

The total capacitance of the diode is the sum of  $C_j$  and  $C_d$ :

$$C = C_i + C_d \tag{6.68}$$

Due to their unique voltage dependencies, in an ideal diode  $C_j$  dominates in reverse bias and small forward bias and  $C_d$  prevails in strong forward bias. This is illustrated in Fig. 6.27.

Exercise 6.5: Consider a pn diode identical to that of Exercises 6.1-6.4. Note again that the p- and n-regions are "long" from the minority carrier point of view. At room temperature and with an applied forward bias of  $V=0.6\ V$ , estimate a) the charge density stored in the two quasi-neutral regions, and b) the diffusion capacitance.

a) In exercise 6.5 we obtained the magnitude of the current density injected into each QNR of this diode at this bias point. We also determined the minority carrier lifetimes. With these results, the fastest way to determine the charge stored in each QNR is using Eqs. 6.52 and 6.53. For the p-QNR, the stored charge per unit area is:

$$Q_p = \tau_e A J_e(-x_p) = 2.3 \times 10^{-6} \text{ s} \times 10^{-7} \text{ cm}^2 \times 6.0 \times 10^{-4} \text{ A/cm}^2 = 1.4 \times 10^{-16} \text{ C}$$

For the n-QNR, the stored charge per unit area is: